Event Details:

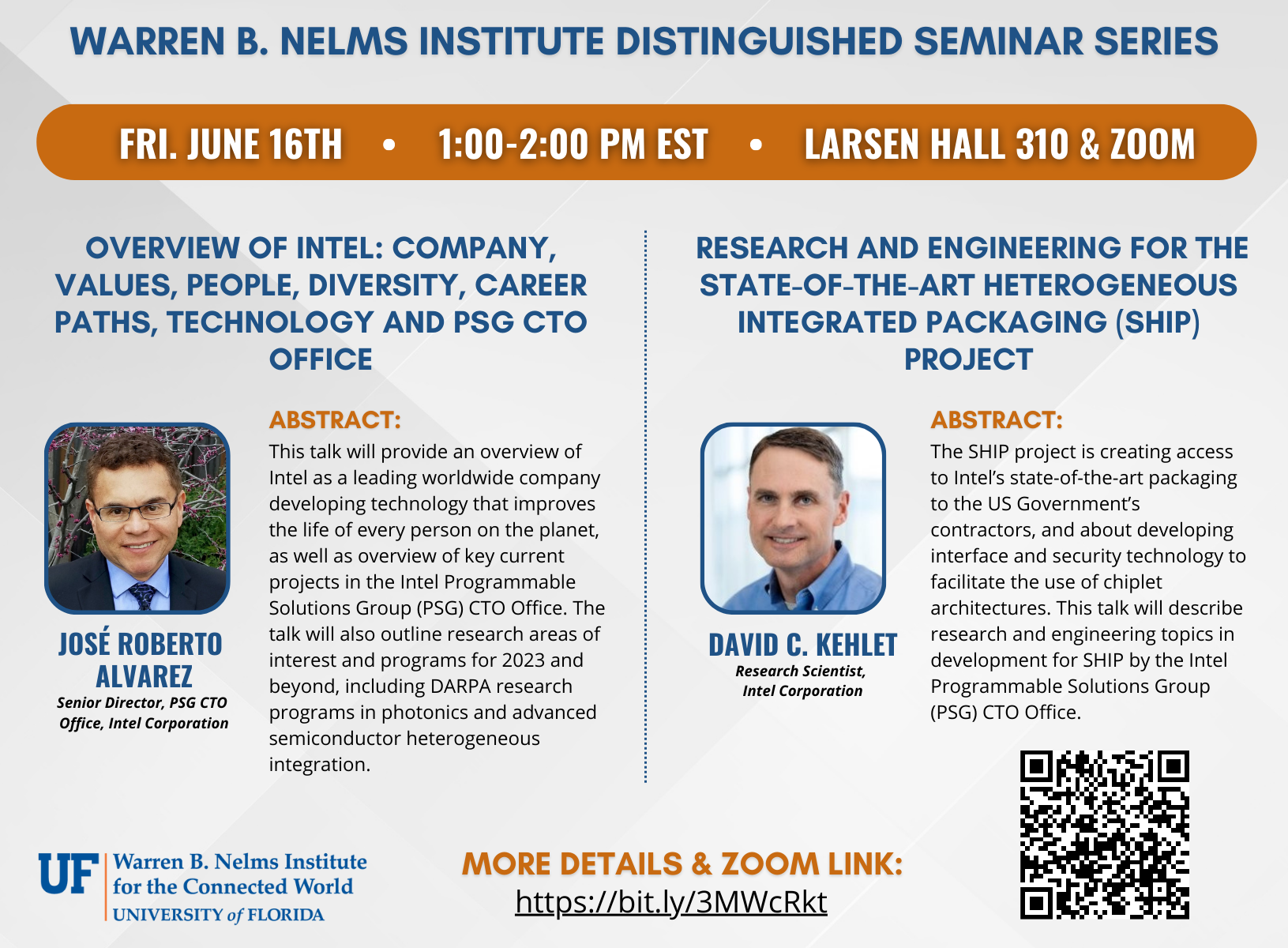

Date: Friday, June 16, 2023

Time: 1:00 – 2:00pm EST

Location: Larsen Hall, Room 310 & Zoom

Hosted By: Dr. Swarup Bhunia

Watch the Seminar:

Overview of Intel: Company, Values, People, Diversity, Career Paths, Technology and PSG CTO Office

Presented by José Roberto Alvarez, Senior Director, PSG CTO Office, Intel Corporation

Abstract:

This talk will provide an overview of Intel as a leading worldwide company developing technology that improves the life of every person on the planet, as well as overview of key current projects in the Intel Programmable Solutions Group (PSG) CTO Office. The talk will also outline research areas of interest and programs for 2023 and beyond, including DARPA research programs in photonics and advanced semiconductor heterogeneous integration.

Bio:

José Roberto Alvarez is Senior Director at Intel Programmable Solutions Group in San Jose, California, where he leads the PSG CTO Office, defining and implementing longterm FPGA research strategy and roadmaps. He started his career at Philips Laboratories and throughout his career he has architected, designed, and implemented technology products for a variety of industries including semiconductors, video broadcast, consumer, cinematic post-production and computer graphics for companies including Philips, Broadcom, Maxim, Xilinx, and four successful start-ups in Silicon Valley. He has actively participated in major industry inflection points in the last 25 years, most notably in the development of multiple video coding standards, desktop video graphics, and advanced FPGA technologies and platforms. He was co-chair of the MPEG MP20 Roadmap group, organizing many worldwide workshops in VR/AR immersive technologies and was inducted into the MPEG Hall of Fame. His research interests include FPGA advanced architectures and development tools, AI/ML domain-specific architectures, immersive media technologies, volumetric coding, semiconductor heterogenous systems integration and optical interfaces. Mr. Alvarez earned bachelor’s and master’s degrees in Electrical Engineering with distinction from The City University of New York. His work has been granted 54 patents.

RESEARCH AND ENGINEERING FOR THE STATE-OF-THE-ART HETEROGENEOUS INTEGRATED PACKAGING (SHIP) PROJECT

Presented by David C. Kehlet, Research Scientist, Intel

Abstract:

The SHIP project is creating access to Intel’s state-of-the-art packaging to the US Government’s contractors, and about developing interface and security technology to facilitate the use of chiplet architectures. This talk will describe research and engineering topics in development for SHIP by the Intel Programmable Solutions Group (PSG) CTO Office.

Bio:

David Kehlet is a researcher at Intel working on pathfinding for programmable logic technologies. David is currently developing chiplet technologies to enable a new model of electronic system development, and is Principal Investigator of the US Government’s State-of-the-art Heterogeneous Integrated Packaging (SHIP) Chiplet Design Technologies project. Earlier at Intel, David was Vice President of IP Engineering, developing SERDES chiplets, communications protocols, signal processing, and memory interfaces on Intel’s programmable logic devices. David’s team developed the FPGA industry’s first HBM2 enabled device and the first FPGA with 56Gbps SERDES. David earned BS and MS Electrical Engineering degrees from Stanford University and holds 19 patents.

David Kehlet is a researcher at Intel working on pathfinding for programmable logic technologies. David is currently developing chiplet technologies to enable a new model of electronic system development, and is Principal Investigator of the US Government’s State-of-the-art Heterogeneous Integrated Packaging (SHIP) Chiplet Design Technologies project. Earlier at Intel, David was Vice President of IP Engineering, developing SERDES chiplets, communications protocols, signal processing, and memory interfaces on Intel’s programmable logic devices. David’s team developed the FPGA industry’s first HBM2 enabled device and the first FPGA with 56Gbps SERDES. David earned BS and MS Electrical Engineering degrees from Stanford University and holds 19 patents.