Prabuddha Chakraborty, a PhD student in the Department of Electrical and Computer Engineering at the University of Florida, has won first place in the semifinals of TTTC’s E. J. McCluskey Best Doctoral Thesis Award at IEEE VLSI Test Symposium 2022 (VTS 22).

Chakraborty will now advance to the finals round of the competition, which will take place at the International Test Conference (ITC) 2022 on September 25-30. He will compete against three other finalists selected from the IEEE European Test Symposium (ETS), the IEEE Latin American Test Symposium (LATS), and the IEEE Asian Test Symposium (ATS).

Chakraborty is advised by Dr. Swarup Bhunia, Semmoto Endowed Professor of IoT and Director of the Warren B. Nelms Institute.

Named after Prof. E.J. McCluskey, a key contributor to the field of test technology, the 2022 TTTC’s Doctoral Thesis Award serves the purpose to promote the most impactful doctoral student work, to provide the students with exposure to the community and the prospective employers, and to support interaction between academia and industry in the field of test technology.

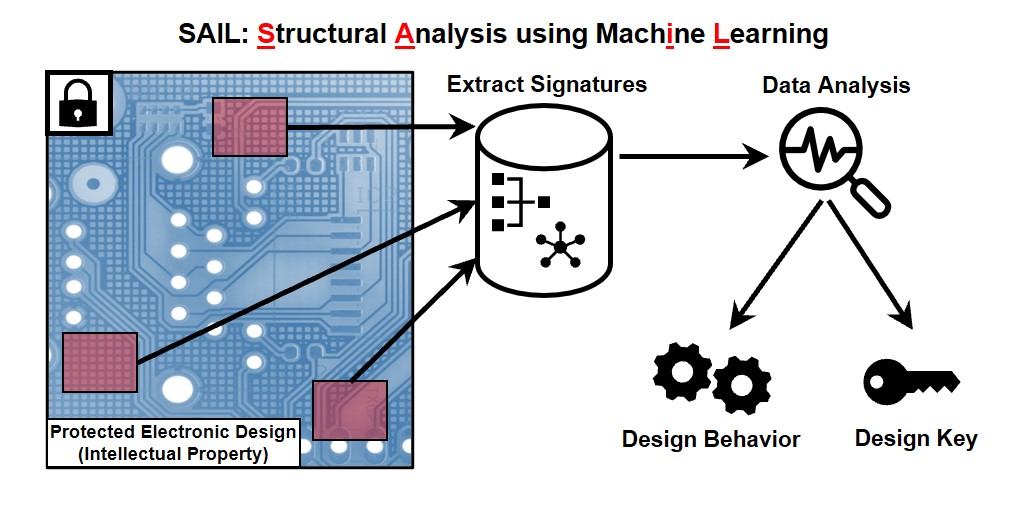

At VTS 22 on April 22, 2022, Chakraborty virtually presented his thesis to a panel of expert academia and industry judges. He competed against seven other shortlisted doctoral students selected by the panel of experts. The title of his talk was “AI-Driven Assurance of Hardware IP against Reverse Engineering Attacks.”

“The proposed attacks, corresponding metrics, and the learning-guided defence strategy have created a new pathway for future research towards logic locking techniques that are resilient against both structural and functional attacks.” – Prabuddha Chakraborty

Abstract:

- Developed an AI-driven attack/evaluation framework for analyzing the effectiveness of structural security of IPs introduced by state-of-the-art LL techniques.

- Proposed a set of well-defined mathematical metrics for quantifying the structural security of a locked IP.

- Developed a learning-driven scalable logic locking framework capable of defending against structural attacks as well as other known attacks.